Session #6: Synthesis & Physical Design¶

Homework¶

- Synthesize your design — review gate count and check for unintended latches

- Run place and route flow

- Analyze timing reports — identify and fix any violations

- Generate GDS and review layout in KLayout

Introduction¶

I had to miss class again, due to teaching my own class. I watcehd the recorded video HERE

Verilog RTL -> [Synethesis] -> Gate Netlist -> Place & Route -> GDS

Note

1000’s of people configure the compiler when doing chip design.

Note

reg are for inside blocks and wire are for outside block.

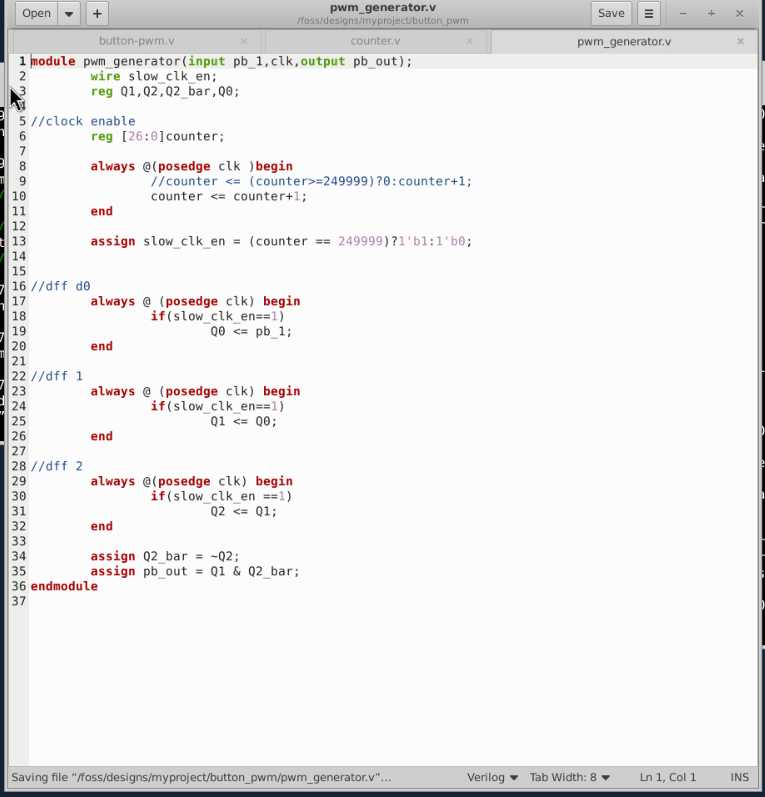

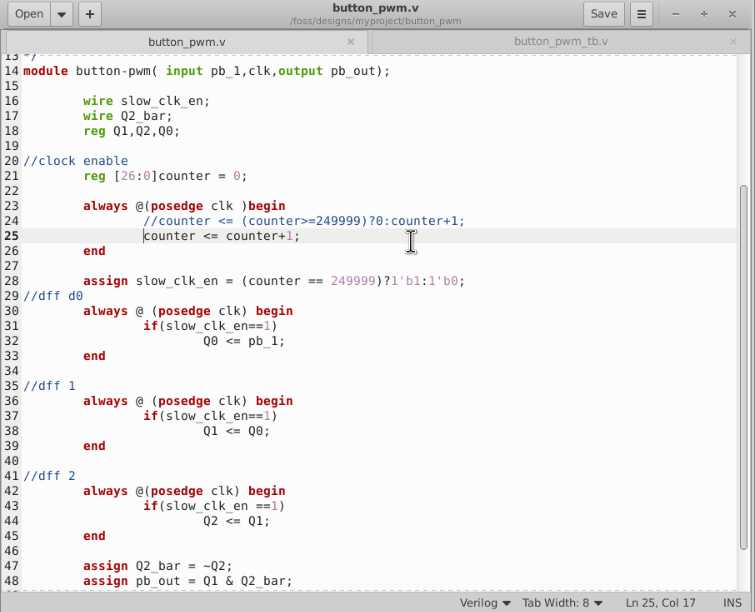

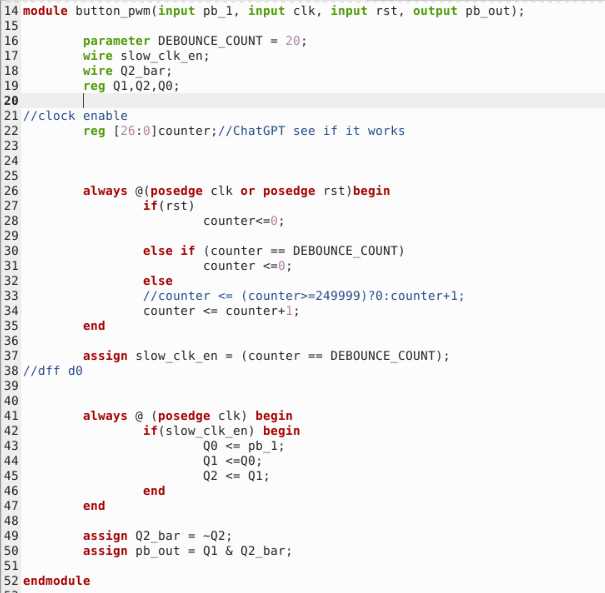

Verilog code for PWM Generator¶

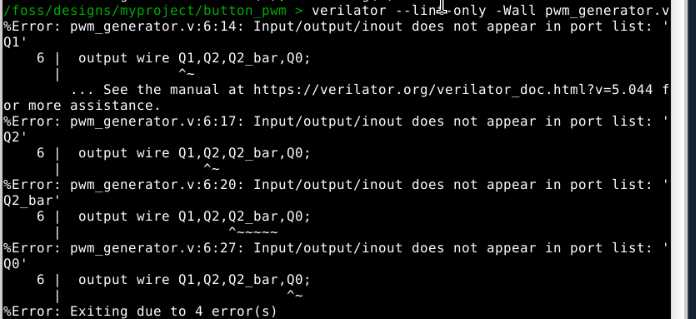

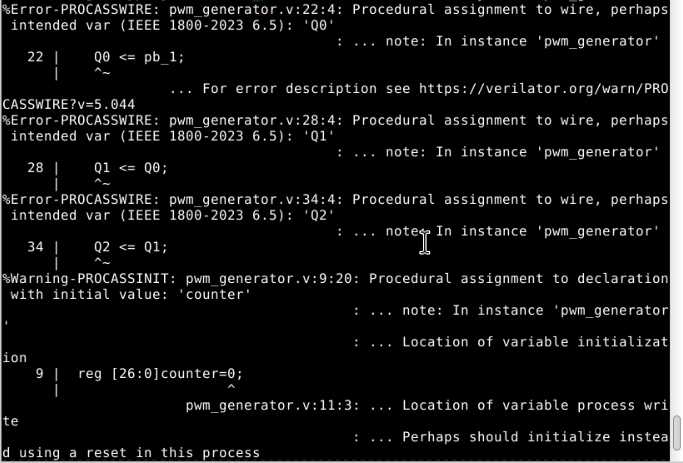

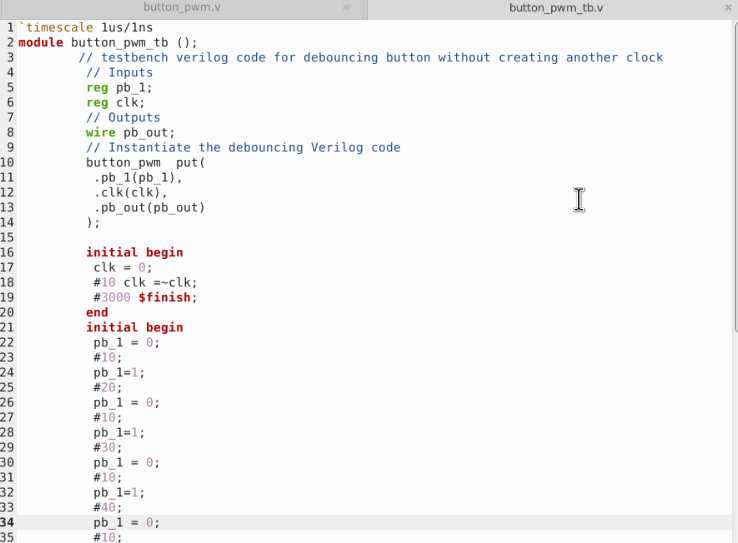

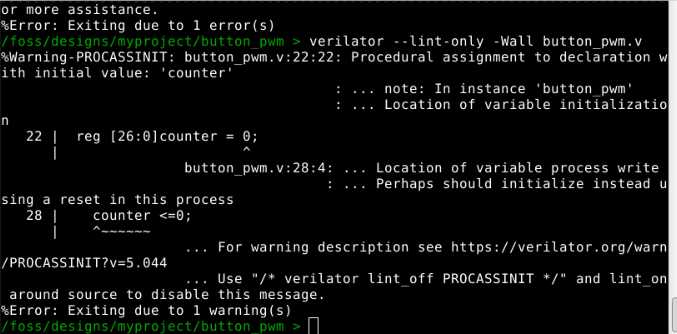

First Error

Second Error

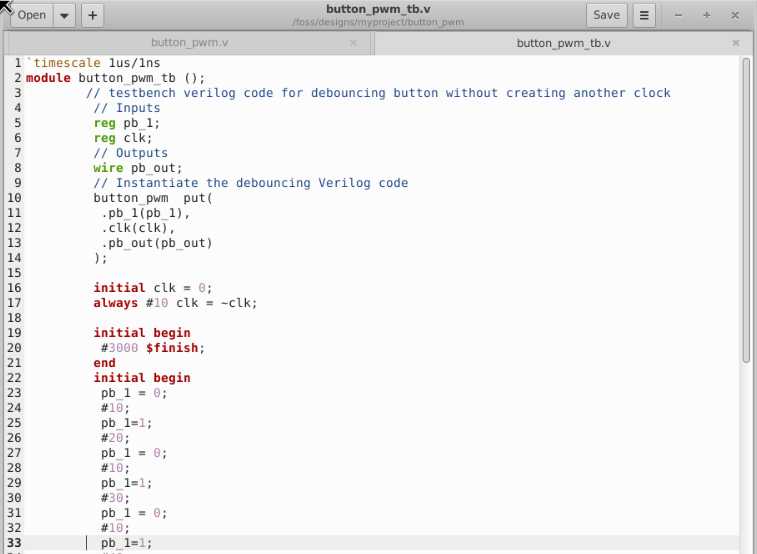

Ventilator passed code

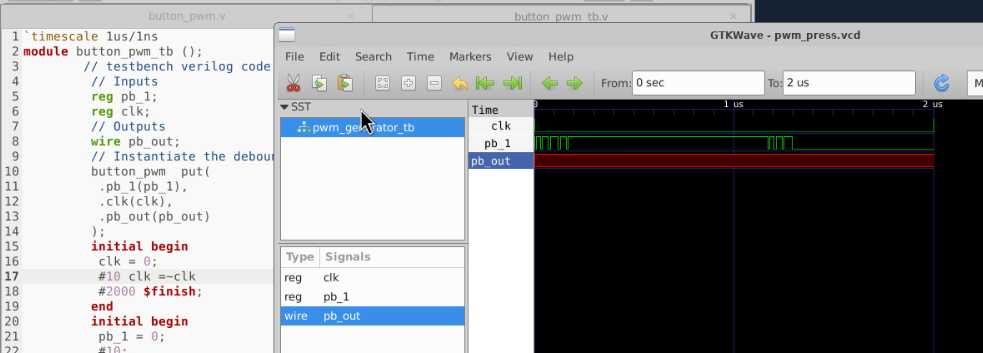

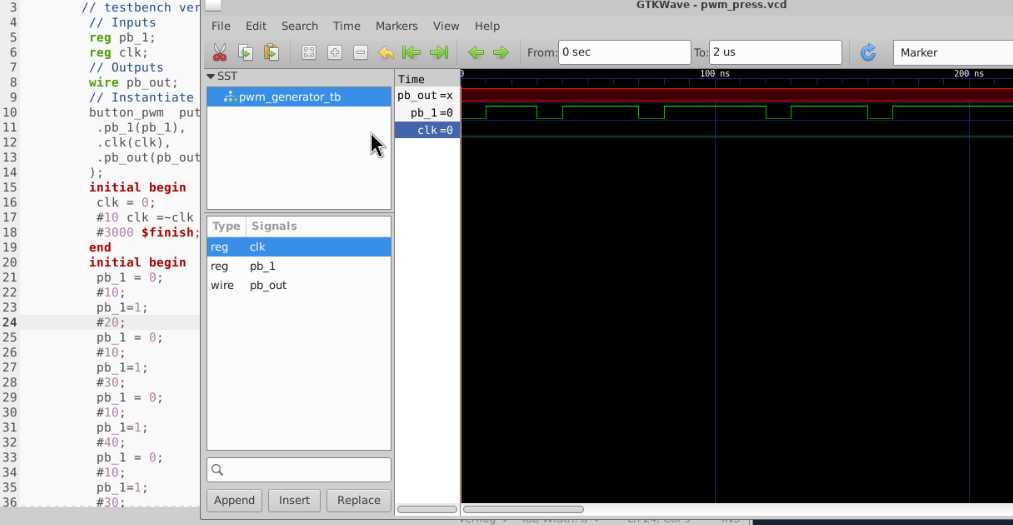

TB

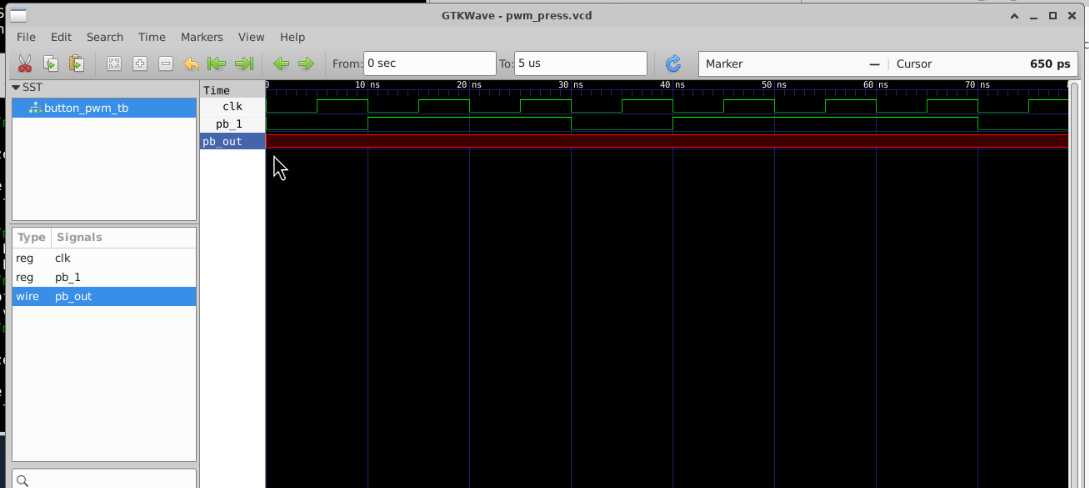

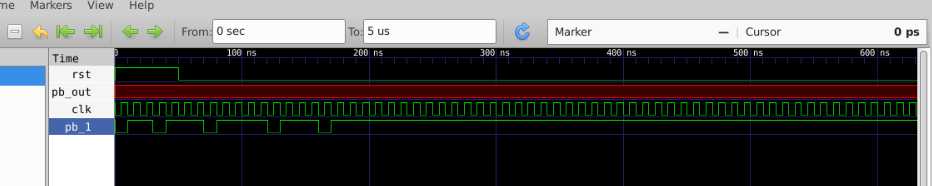

GTKWave: The vcd file was incredible large, had to remove it. Don’t know why YET!

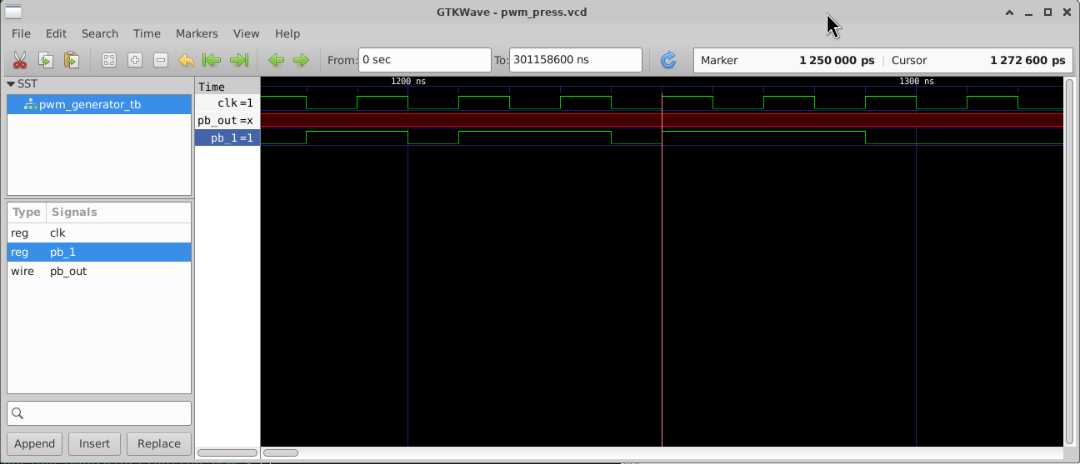

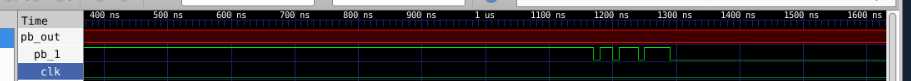

Below is the visual of the vcd file. I notice the

Found this little nugget of information.

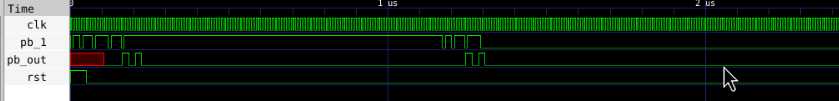

I think the pb_out has the incorrect timing. so I changed the time scale. The pb_out is still reading x and the graph is red. The signal is not getting to the button. I no long think it is a time issue and think it is a construct logic issue.

Read this about the counter (here)[https://www.fpga4student.com/2017/04/simple-debouncing-verilog-code-for.html]

Not exactly the file I wanted, however I decided to move on with the rest of the assignment.

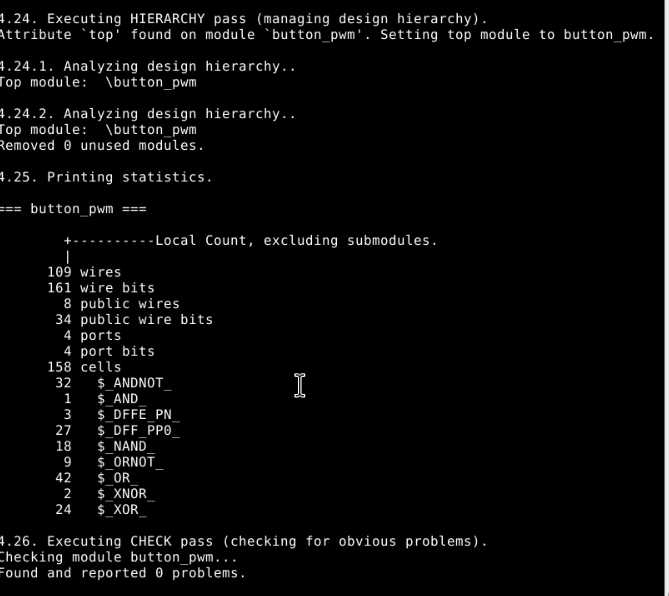

Synthesize¶

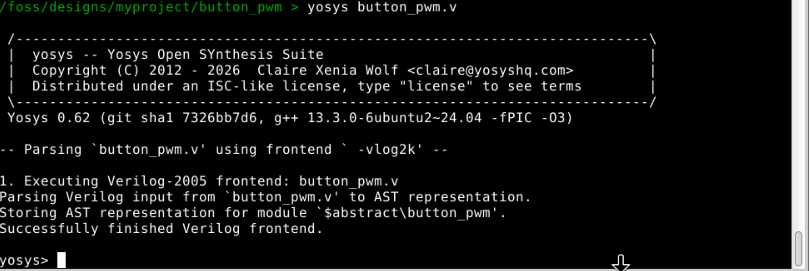

Yosys

ok, did not know what to expect. Since this was an extremely simple verilog file not much to look at yet.

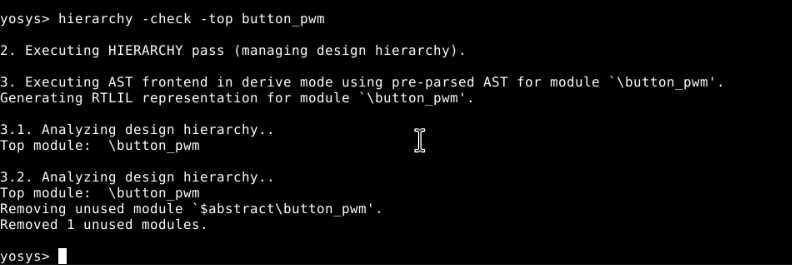

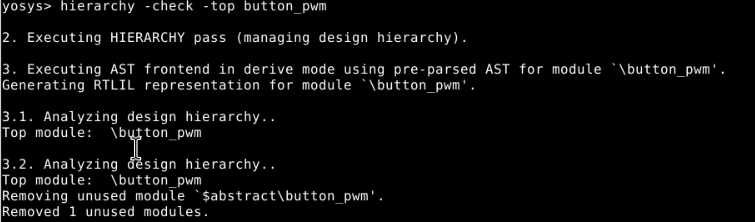

Heirachy check

hierarchy - check -top button_pwm

Seem to run into a problem I could not write in the yosys termial anymore. I stop the terminal and started another one.

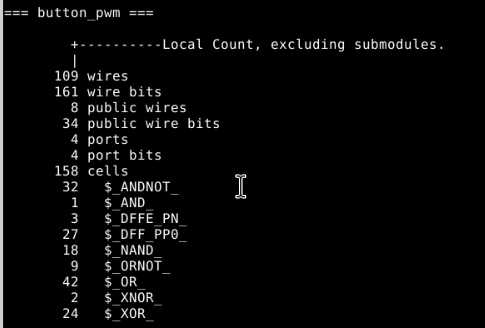

Yes I can sse the wire, ports, cells, gates, and other things.

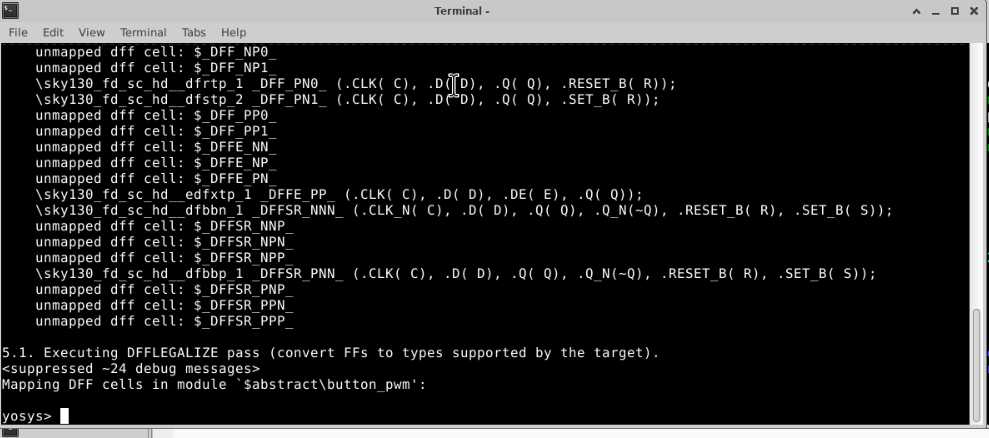

some unmapped and some mapped

Well this did not work.

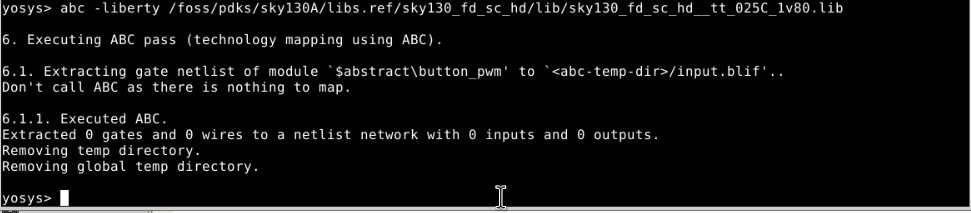

I thought it may not have worked because I had to stop everything an come back so I came back in the morning and ran yosys commands and it seems like a success.

```yosys button_pwm.v”

hierachy -check -top button_pwm

synth -top button_pwm

write_verilog -noattr synth.v

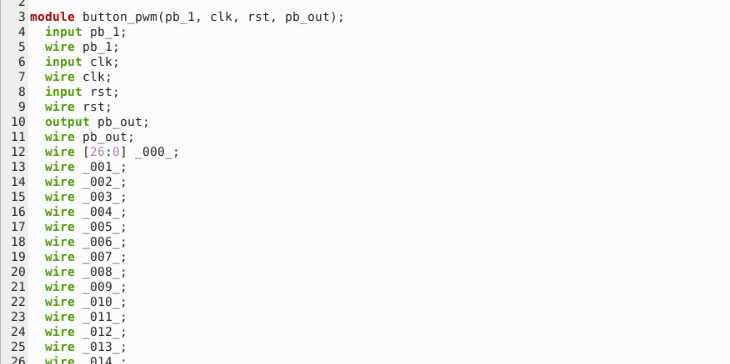

I check for the synth.v file and low and behold there was a verilog file.

It looks like sucess for the step.

Route Flow¶

Started the route and flow process. Hit a snag reading the synth.v file.

Show code

``` python # Setup import matplotlib.pyplot as plt import matplotlib.patches as patches from matplotlib.patches import FancyBboxPatch, Rectangle, FancyArrowPatch import numpy as np print("Setup complete.") ```Show code

# Setup

import matplotlib.pyplot as plt

import numpy as np

print("Setup complete.")

Timing Analysis¶

GDS Generation¶

Resources:¶

- Systhesis & Physical Design Class

- Systhesis & Physical Design Video

- https://excalidraw.com/

- https://mail.google.com/mail/u/1/#inbox/FMfcgzQfCMqbkmqRTbvgBgnDVHjXZdNx

- https://oscilloscope.fhdm.xyz/

- (Verilog Motor Control)[https://eureka.patsnap.com/article/fpga-programming-for-motor-control-vhdlverilog-examples]

- https://www.fpga4student.com/2017/04/simple-debouncing-verilog-code-for.html