Home¶

Hello, I’m Grecia! 👋¶

I’m an electronic and systems engineer from Santa Cruz de la Sierra, Bolivia. I work at FabLab Santa Cruz a research organization where I lead science, technology, and innovation projects with local impact.

I joined this course because I wanted to understand the complete chip design pipeline from a Verilog description all the way to a physical GDS file ready for fabrication. After working with microcontrollers and embedded systems for years, I wanted to go one level deeper: designing the chip itself.

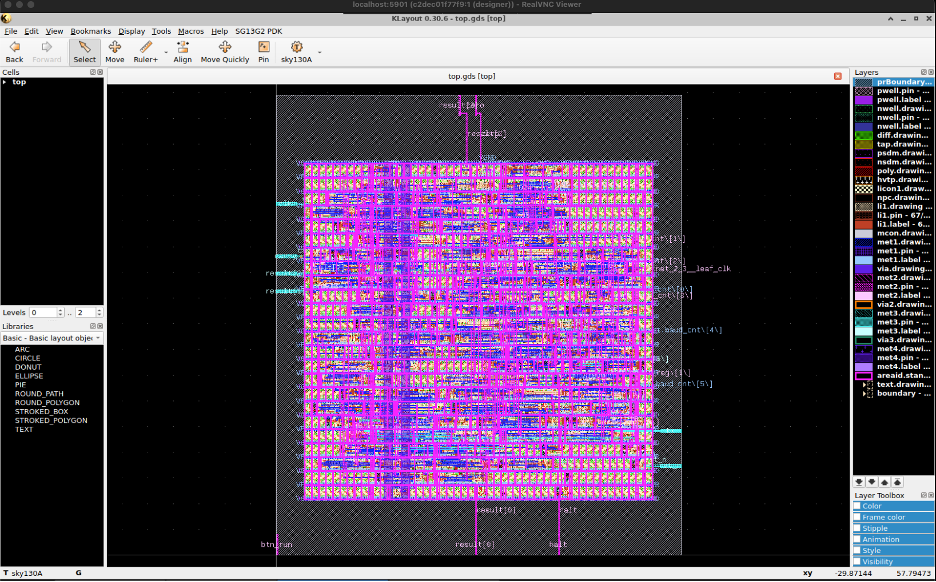

My final project is the APOLLO-4G a 4-bit CPU inspired by the Intel 4004 from 1971, the same year as the Apollo 14 mission. It executes a Fibonacci sequence program stored in ROM and transmits the results via UART, designed and verified in Sky130A 130nm technology.

Weekly Assignments¶

- Session 1 — Introduction & Development Pipeline

- Session 2 — Analog Basics

- Session 3 — Schematic Design & Simulation

- Session 4 — Layout & Fabrication

- Session 5 — RTL Design & Verification

- Session 6 — Synthesis & Physical Design

- Session 7 — Packaging & Board Design

Final Project — APOLLO-4G¶

In this project I designed a complete 4-bit CPU following the full open-source chip design flow from Verilog RTL to synthesis, place and route, DRC, LVS, and final GDS generation using Sky130A 130nm technology and LibreLane.

The CPU executes a real stored program: the Fibonacci sequence. It includes an ALU, a ROM with the program, a control unit that decodes instructions, a UART transmitter that sends results to a terminal, and a debounce module for the input button.

Beyond the chip itself, this project helped me understand how an idea can evolve from a concept into a real silicon layout and it gave me a new perspective on what it means to design hardware at the transistor level, from Bolivia. 🇧🇴